芯创前线▎从IEDM 2023 看集成电路创新前沿机遇

由 IEEE 电子器件协会主办的IEEE IEDM 会议,是世界上规模最大、最具影响力的论坛,旨在揭示晶体管和相关微/纳米电子器件的突破性进展。第 69 届 IEEE IEDM 年会的主题是 "基于 60 年 CMOS 技术的智能世界设备"。会议将于 2023 年 12 月 9 日至 13 日在旧金山联合广场希尔顿酒店举行。

今年的技术亮点包括四场专注于关键新兴技术的焦点会议:

智能传感器的神经形态计算(第 7 场会议)——人们对神经形态计算的兴趣与日俱增,其中电子设备和系统旨在模拟大脑的工作方式。希望这将为困难的计算挑战提供新的、更好的解决方案。本次焦点会议包含描述神经形态计算和智能传感器最新进展的特邀论文。

1、The Case for Hybrid Analog Neuro morphic Chips Based on Silicon and

2DMaterials, G.Iannaccone, Università di Pisa and Quantavis s.r.l.

2、Case Study of Tactile Sensors: System-Level Approach to Analog In-Sensor Computing, M-Y Mun,Samsung

3、Intelligent Vision Sensor and Edge

Computing Envisage the Future, R.

Eki, Sony

4、Live-Cell Imaging with Integrated

Capacitive Sensor Arrays, J. Rosenstein, Brown Univ./Northeastern

Univ./Raytheon/Boston Univ.

5、Towards CMOS Capacitance Sensors for DNA Origami Characterization, M. Dandin, Carnegie Mellon Univ.

6、Scalable Biosensors Using Standard

CMOS Process, U. Noyan, University of Maryland

未来生成人工智能的逻辑、内存、封装和系统技术(第 15 场会议)——生成式人工智能 (AI) 最近备受关注,它具有提高人类许多领域的生产力和效率的潜力。然而,创建未来生成人工智能系统所需的逻辑、内存和其他设备是艰巨的技术挑战。本次焦点会议涵盖了人工智能计算的系统需求、技术障碍和解决方案。

1、Generative AI on a Budget: Processing Transformer-based Neural Networks at the Edge, Y. Tanurhan, Synopsys

2、Design of Analog-AI Hardware Accelerators for Transformer-based Language Models, G. Burr, IBM

3、The Era of Generative Artificial Intelligence: In-Memory Computing Perspective, K. Sohn, Samsung

4、Innovations For Energy-Efficient Generative AI, S. Naffziger, AMD

5、Beyond Exascale: A Paradigm Shift for AI and HPC, W. Gomes, Intel

6、Advanced Packaging Technologies in Memory Applications for the Future Generative AI Era, K-I. Moon, SK Hynix

7、NVDRAM: A 32Gb Dual-Layer 3D Stacked Non-Volatile Ferroelectric Memory with Near-DRAM Performance for Demanding AI Workloads, N. Ramaswamy, Micron

通过晶圆键合及相关技术实现下一代逻辑和存储器的 3D 堆叠(第 19 场会议)——随着前沿 CMOS 器件的特征尺寸接近原子尺寸,传统的缩放变得更加困难和昂贵。满足不断增长的计算和人工智能工作负载的需求,同时仍然实现传统 PPAC 的扩展优势(性能、功耗、面积和成本)的一种方法是以 3D 配置垂直堆叠集成电路。

1、Process Innovations for Future Technology Nodes with Backside Power Delivery and 3D Device Stacking, M. Kobrinsky, Intel

2、Backside Power Delivery: Game Changer and Key Enabler of Advanced Logic Scaling and New STCO Opportunities, A. Veloso, IMEC

Thermal Dissipation in Stacked Devices, W-Y. Woon, TSMC

Ultimate Layer Stacking Technology for High-Density Sequential 3D Integration, I. Radu, Soitec

CMOS Directly Bonded to Array (CBA) Technology for Future 3D Flash Memory, M. Tagami, Kioxia

Wafer Bonding as Next-Generation Scaling Booster, P. Lindner, EV Group

半导体器件技术和制造的可持续性(第 28 场会议)–本次焦点会议讨论设备技术和制造的可持续性,因为更有效地利用地球有限的资源并减少相关的环境影响从未如此重要。

1、Cradle-to-Gate Life Cycle Assessment of CMOS Logic Technologies, L. Boakes, IMEC

2、Sustainability-Aware Technology Development at Applied Materials, B. Gross, Applied Materials

3、EUV Energy Efficiency, T. Thijssen, ASML

4、Sustainable Environmental Technologies for Advanced Semiconductor Manufacturing Intelligent FAB,H-C. Lee, Samsung

5、Modeling 300mm Wafer Fab Carbon Emissions, S. Jones, TechInsights

6、eveloping Sustainable Technologies for a More Sustainable Future, S. Nicoleau, ST Microelectronics

一、CMOS 缩放:

CFET和 2D 沟道 FET

基于纳米片的晶体管和由纳米片构建的 3D 互补 FET (CFET) 是继续摩尔定律扩展的关键。纳米片是环栅 (GAA) 晶体管架构,其中硅沟道堆栈完全被栅极包围。它们提供比 FinFET 更好的静电控制、相对较高的驱动电流和可变宽度。CFET 架构是高度集成的 3D 设计,其中 n-FET 和 p-FET 纳米片堆叠在一起。这些堆叠器件可以单片构建(在一个晶圆上),也可以顺序构建(构建在单独的晶圆上,然后转移和集成)。在 IEDM 上,许多论文将推动这些领域的最新技术发展。其中包括台积电 (TSMC) 和英特尔 (Intel) 的论文,讨论了近期扩展硅 (Si) CMOS 技术的方法:

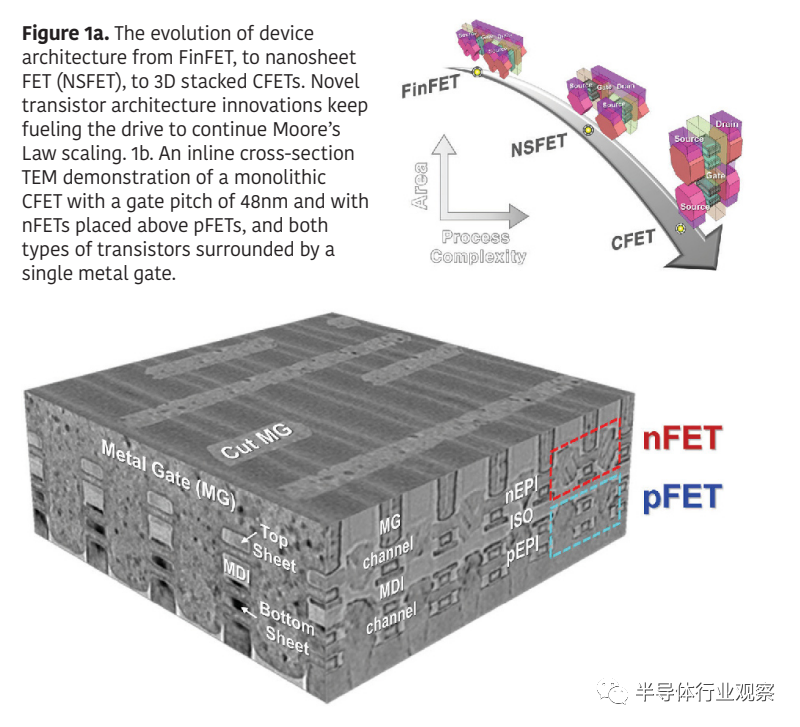

实用的单片 CFET 架构:在最新的新闻论文中,台积电研究人员将推出他们所谓的实用的单片 CFET 架构方法,用于逻辑技术扩展。它具有 48nm 栅极间距堆叠式 n-FET-on p-FET 硅纳米片晶体管。这些表现出高通态电流/低亚阈值泄漏,导致令人印象深刻的开/关流动比率(六个数量级)。它们还表现出相对较高的良率,FET 存活率(survival rate)>90%。尽管之前的工作表明功能性 CFET 器件可以在 300mm 晶圆上构建,但这些器件的栅极间距对于未来的扩展来说太大了。在这项工作中,通过垂直堆叠的 n/p 源极-漏极 (SD) 外延实现了更相关的 48 nm 栅极间距,包括中间电介质隔离、内部隔离物和 n/p SD 隔离。虽然仍必须集成其他基本功能才能释放 CFET 技术的潜力,但这项工作为实现这一目标铺平了道路。(Paper 29.6, “Complementary Field-Effect Tran sistor (CFET) Demonstration at 48nm Gate Pitch for Future Logic Tech nology Scaling,” S. Liao et al, TSMC)

图1a.器件架构从 FinFET 到纳米片 FET (NSFET),再到 3D 堆叠 CFET。新颖的晶体管架构创新不断推动摩尔定律的扩展。1b.栅极间距为 48 nm、nFET 放置在 pFET 上方的单片 CFET 的内联横截面 TEM 演示,两种类型的晶体管均被单个金属栅极包围。

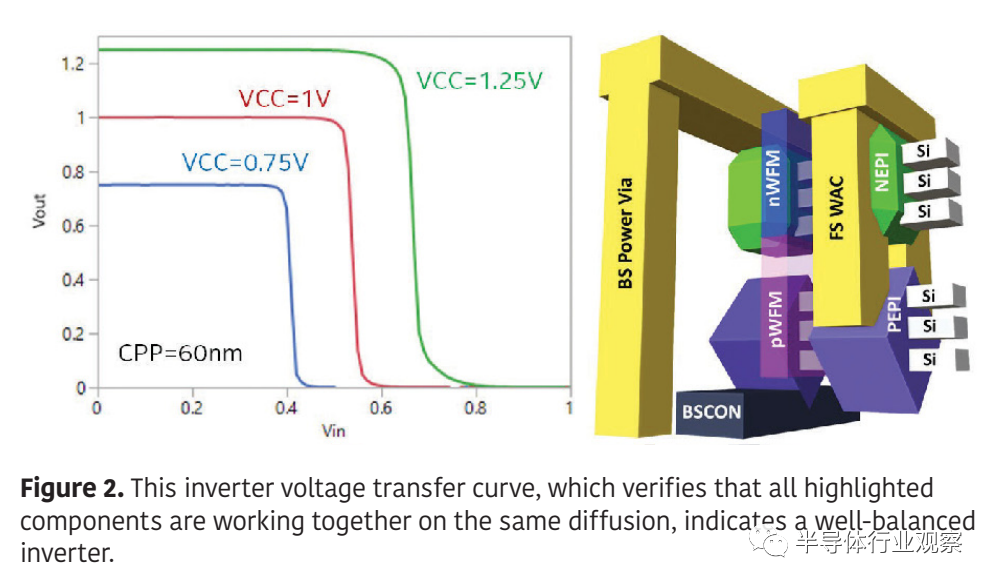

基于 CFET 的 CMOS Inverter:与此同时,英特尔研究人员将讨论他们构建的 3D 单片 CFET 器件,该器件由 3 个 p-FET na no 纳米带顶部的 3 个 n-FET 纳米带组成,它们之间的垂直间距为 30 纳米。他们使用该器件以 60nm 栅极间距构建功能齐全的Inverter(测试电路)(图2),这在业界尚属首次。该器件还采用垂直堆叠双S/D 外延技术;连接n型和p型晶体管的双金属功函数栅叠层;以及与背面供电和直接背面器件触点的集成。研究人员还将描述纳米带“减少”过程,用于需要数量不等的 n-MOS/p-MOS 器件。这项工作有助于加深对逻辑和 SRAM 应用扩展 CFET 潜力的理解,并了解关键的工艺推动因素。

(Paper 29.2, “Demonstration of a Stacked CMOS Inverter at 60nm Gate Pitch with Power Via and Direct Backside Device Contacts’M. Radosavljevic et al,Intel)

图2.该inverter的电压传输曲线验证了所有突出显示的组件都在同一扩散上一起工作,表明逆变器平衡良好。

其他论文描述了更多探索性研究,超越了基于硅的 CMOS 技术:

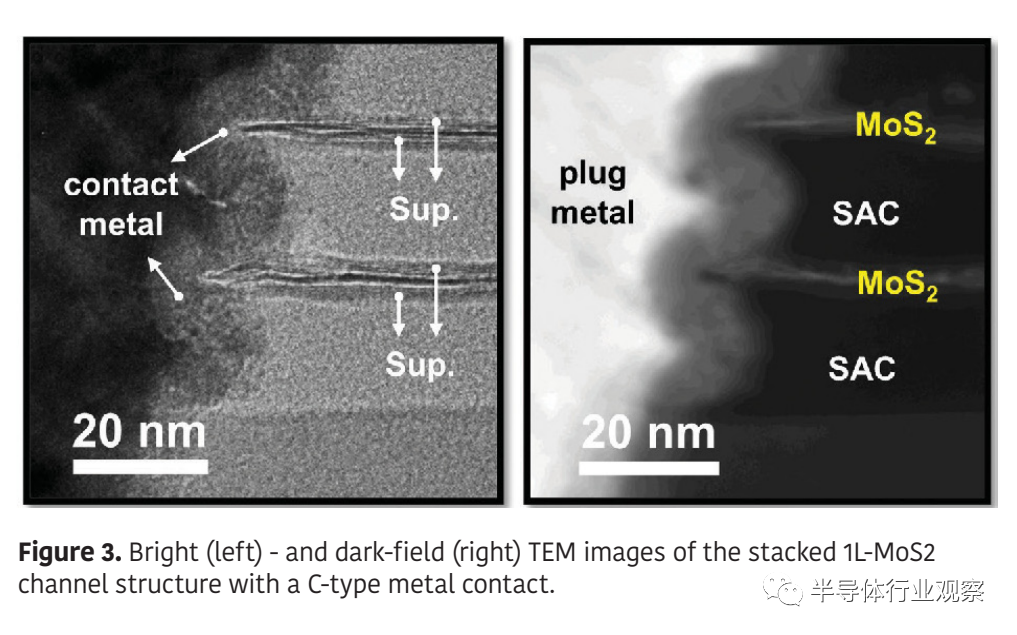

记录具有TMD沟道的堆叠NMOS纳米片的结果:目前,纳米片缩放是通过减薄Si沟道来实现的,但正在努力寻找使用超薄过渡金属二硫化物(TMD)作为沟道材料的实用方法。(MoS2 等 TMD 被称为单层或 2D 材料,因为它们只有原子层厚度。)台积电领导的团队将讨论两个具有 MoS2 沟道的堆叠 NMOS 纳米片的前所未有的性能(图 3)。

图 3. 具有 C 型金属接触的堆叠 1L-MoS2 沟道结构的亮场(左)和暗场(右)TEM 图像。

40nm栅长NMOS器件表现出正阈值电压(VTH~1.0V);高导通电流(VDS = 1 V 时 ION ~370 μA/μm);大开/关比(1E8);低接触电阻的结果是新颖的 C 形环绕接触,提供更大的接触面积和栅极堆叠优化。这些器件表现出可接受的机械稳定性,但研究人员表示,需要进行更多研究来减少 MoS2 沟道中缺陷的产生。 (Paper 2.1, “Monolayer-MoS2 Stacked Nanosheet Channel with C-type Metal Contact," Y-Y Chung et al,TSMC/Nat’l Yang Ming Chiao Tung Univ./National Applied Research Laboratories)

第一个真正的 2D CMOS 演示:每个极性的 FET 器件(n-FET 和 p-FET)必须提供匹配的性能,以便 CMOS 逻辑器件正常工作。但是,虽然 MoS2 是一种适合 n 型器件的 TMD 材料,但它不适用于 p 型器件,而 TMD 材料 WSe2 更适合 p 型器件。此外,这两种极薄的材料都必须足够坚固,能够承受典型的制造工艺。TSMC 领导的团队将在业界率先描述分别使用这两种 TMD 沟道材料制造的匹配良好的 n MOS 晶体管和 p MOS 晶体管。他们通过在蓝宝石上单独生长这些高尺寸(~50nm 沟道长度)和高电流密度材料,然后将它们逐个芯片转移到 300mm 硅晶圆上进行集成,展示了这些材料的鲁棒性。在此转移过程之后,器件的性能几乎没有改变,n-FET 和 p-FET (VDS = 1V) 在相同的栅极过驱动下具有高输出电流 (~410 μA/μm)。此外,p-FET 迁移率达到了创纪录的高水平(~30 cm² /Vs)。 (Paper10.1,“Status and Performance of Integration Modules Toward Scaled CMOS with Transition Metal Dichalcogenide Channel,” A-S Chou et al, TSMC/Nat’l Taiwan Univ/ Nat’l Yang Ming Chiao Tung Univ.)

二、存储

密集、快速、低电压、高耐久 STT-MRAM:非易失性存储器在电源关闭时保留数据,这使得它们在汽车等嵌入式应用中非常有用。闪存一直是嵌入式的首选,但在先进节点上却表现不佳。非易失性磁存储器(磁阻 RAM 或 MRAM)将数据存储为磁性状态,而不是电荷,并且已进入嵌入式应用领域。一种称为自旋转移扭矩 MRAM (STT-MRAM) 的类型提供快速写入速度、极高密度、低功耗操作和长耐用性的潜力。在 IEDM 上,台积电领导的团队将描述具有 1S1R(1 个选择器/1 个电阻器)交叉点阵列架构的 STT-MRAM,其密度是传统 1T1R(1 个晶体管/1 个电阻器)的两倍以上(>2.2 倍)设计采用 16nm 技术节点。使这一切成为可能的是使用专门设计的选择器材料 SiNGeCTe。STT-MRAM 展示了低电压运行 (<1.8V);高速开关(关-开/开-关转换分别为 2.5ns/3ns);以及出色的读/写耐久性(分别>1e9/>1e6 周期)。据说该架构适用于可堆叠 3D 内存阵列。 (Paper 21.5, “Low Voltage (<1.8V) and High Endurance (>1M) 1-Selec tor/1-STT-MRAM with Ultra-Low (1 ppb) Read Disturb for High Density Embedded Memory Arrays,” E. Am brosi et al, TSMC/Taiwan Semicon ductor Research Institute)

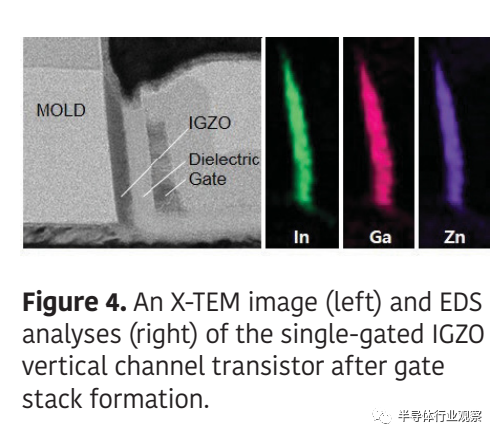

扩展 DRAM 的新方法:DRAM 是电子系统的主力存储器,但将其扩展到传统的 6F2 DRAM 埋置单元阵列布局晶体管极其困难,抑制来自附近单元的“row hammer”电干扰也是如此。但三星研究人员看到了利用 IGZO(氧化铟镓锌)作为沟道材料的垂直沟道晶体管 (VCT) 进一步扩展 DRAM 的机会。(IGZO 具有高电子迁移率、低泄漏、高开/关比,从而降低功耗,并且适合低温处理。)在 IEDM 上,他们将详细介绍 4F2 单沟道的首次成功集成。门控 IGZO-VCT,单片堆叠在核心/外围晶体管顶部,无需晶圆键合(图 4)。他们表示,这些器件适用于 sub-10nm DRAM,具有低漏电流(IOFF <1 fA/cell);亚阈值摆幅 (SS) 为 164 mV/dec,以及足够的阈值电压(85°C 时 VT = -1.73V)。垂直架构还可以完全抑制行锤干扰,因为活动区域不与相邻单元共享。 (Paper 6.3, “Highly Manufacturable, Cost-Effective, and Monolithically Stackable 4F2 Single-Gated IGZO Vertical Channel Transistor (VCT) for sub-10nm DRAM,” D. Ha et al, Samsung)

图 4. 栅堆叠形成后单栅 IGZO 垂直沟道晶体管的 X-TEM 图像(左)和 EDS 分析(右)。

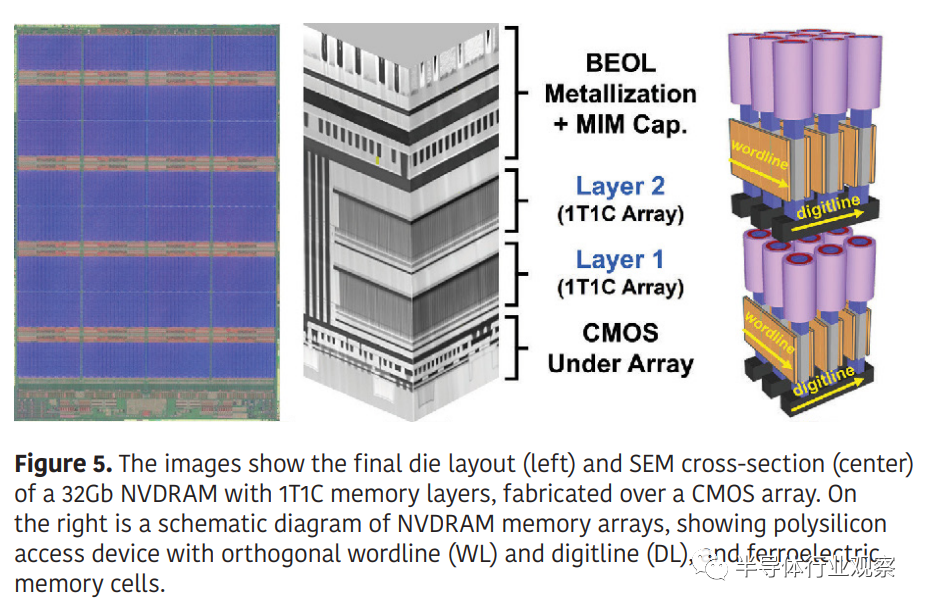

具有类似 DRAM 性能的非易失性铁电体,适用于人工智能和机器学习:人工智能 (AI) 和机器学习 (ML) 应用中使用的数据模型规模快速增长,迫切需要更高带宽的内存解决方案。虽然正在研究近内存计算和内存处理等新的计算模式,但近期最好的机会是为现有的传统计算架构配备更高效的内存,以实现更快的数据移动并适应更大的模型。在今年的生成式 AI 焦点会议上,美光研究人员将推出一种用于这些用途的内存技术,他们称之为 NVDRAM。它是世界上第一个双层、高性能、高密度(32Gb)、可堆叠和非易失性铁电存储器技术(图5)。它结合了铁电存储单元的非易失性、高耐用性和类似 DRAM 的读/写速度和耐用性,并且还超越了 NAND 存储器的保留性能。NVDRAM 使用超大规模 (5.7nm) 铁电电容器作为存储单元,并使用双栅极、可堆叠、多晶硅晶体管作为访问器件。为了实现高存储密度,在 CMOS 电路上方采用 48nm 节距、4F2 架构制造了两个存储层。完整封装良率在 -40°C 至 95°C 范围内得到验证,并且具有 10 年的可靠性(耐用性和保持性)。(Paper 15.7, “NVDRAM: A 32Gb Dual Layer 3D Stacked Non-Volatile Ferroelectric Memory with Near-DRAM Performance for Demanding AI Workloads,” N. Ra maswamy et al, Micron Technology)

3D NAND 的更大存储窗口:非易失性 3D NAND 闪存广泛用于企业、移动和边缘计算应用以及新兴人工智能用例中的数据存储。3D NAND 通常使用带有电荷陷阱氮化物 (CTN) 层的栅极堆叠。这些器件的积极垂直缩放导致位单元密度大幅增加,但代价是写入电压更高,因为栅极控制变得更加困难。这会导致系统级速度降低、单元尺寸增大以及功耗增加。

需要更大的存储器窗口(器件“开”和“关”状态之间的电压差)来增加栅极控制。为了实现更大的存储窗口,铁电(FE)栅极堆栈作为CTN层的可能替代品受到了关注,但要使该技术可行还需要做很多工作。乔治亚理工学院领导的团队首次模拟并实验证明了FE HZO堆叠中间的AI2O3层。它显着增强了器件的内存窗口,从没有AI2O3插入的参考HZO栅极堆栈中的3V到高达7.3 V,提高了2倍。研究人员表示,进一步的建模为实现垂直NAND闪存技术的12V存储窗口提供了一条途径。(Paper 24.1, “Experimental Demonstration and Modeling of a Ferroelectric Gate Stack with a Tunnel Dielectric Insert for NAND Applications,” D. Das et al, Georgia Tech/Samsung)

鉴于人们对神经形态计算领域的兴趣日益浓厚,今年的IEDM会议首次成立了一个专门研究神经形态计算的技术小组委员会。

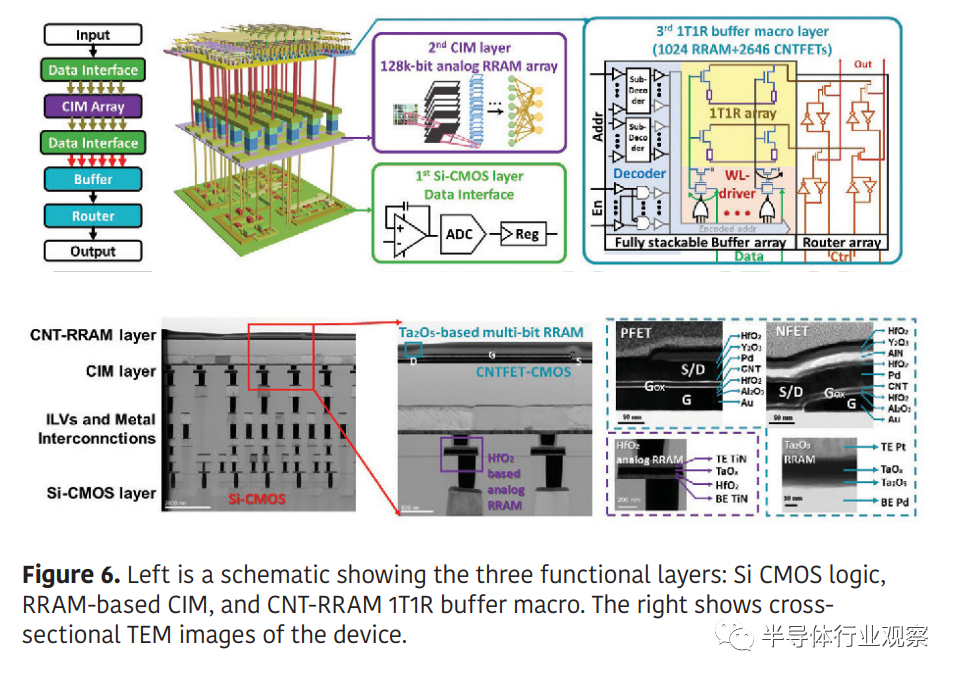

类似GPU的精度,但能耗和推理时间要少得多:大规模人工智能模型对硬件的计算能力和速度的要求不断提高。然而,典型的二维内存计算(CIM)体系结构在用作处理元素的不同CIM阵列层之间存在数据传输瓶颈。这是因为每一层的计算结果必须使用有限带宽的片上总线在CIM阵列和缓冲区之间移动,这大大增加了深度神经网络的整体计算时间。清华大学领导的团队将描述一种单片3D器件架构,该架构将缓冲阵列集成在CIM阵列之上,以及密集的细粒度层间通孔。1kb阵列由三个功能层组成:用于CIM层的128kb基于hfo2的模拟RRAM阵列;用于数据缓存的可堆叠碳纳米管CNT-FET/ ta2o5基RRAM 1T1R缓冲宏层;和Si CMOS逻辑层(图6)。

对所有器件和电路进行了表征,确认每一层都按设计工作,在MLP和ResNET32网络上的图像分类显示,GPU等效准确率为96.5%,能耗降低39倍,推理时间减少49.6倍。(Paper 23.2, “3D Stackable CNTFET/RRAM 1T1R Array with CNT CMOS Peripheral Circuits as BEOL Buffer Macro for Monolithic 3D Integration with Analog RRAM-based Computing-In-Memory,” Y. Zhang et al, Tsinghua Univ./Peking Univ.)

概率推理的硬件演示:前馈神经网络是一种信息只从一层向前移动到下一层,而不是循环的网络,其目标是让输入产生有助于某种预测的输出。前馈神经网络是深度学习推理系统的支柱,但它给传统的计算硬件带来了沉重的计算负担。一个由加州大学圣巴巴拉分校领导的团队将讨论一个深度前馈随机网络的推理系统,该系统产生了迄今为止最快的概率比特(p比特)(比以前的演示快三个数量级)。在他们的系统中,低势垒随机磁隧道结(sMTJ)用于产生概率p位,然后将其路由到现场可编程门阵列(FPGA)电路,以构建CMOS+sMTJ混合计算机。研究人员表示,原型电路的缩放版本可用于加速从深度学习到组合优化的广泛应用。(Paper 12.1, “Hardware Demonstration of Feedforward Stochastic Neural Networks with Fast MTJ-based p-bits,” N. Sanjay Singh et al, UC Santa Barbara/Tohoku Univ.)

三、功率器件

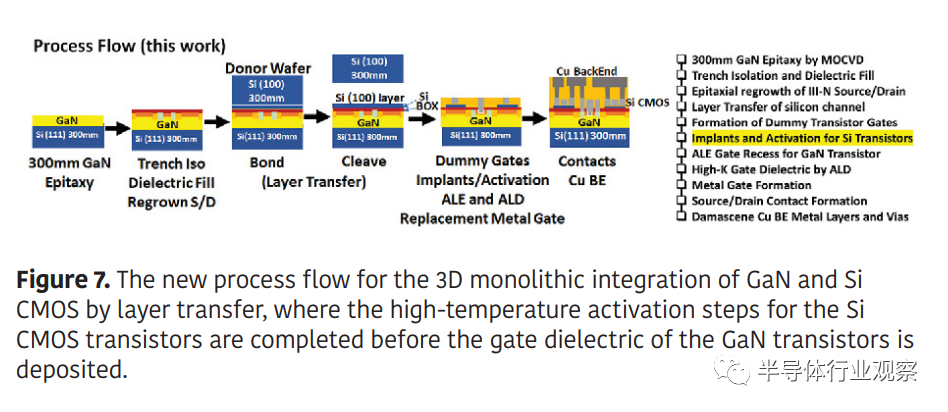

具有CMOS和GaN沟道的功率器件:氮化镓(GaN)器件因其解决数据中心和网络平台的功率密度/效率要求的潜力而引起了人们的极大兴趣。英特尔的研究人员,在他们早期将GaN技术与传统Si CMOS技术集成的基础上,将在IEDM上描述第一款采用300 mm GaN-on-Si技术的集成CMOS驱动器GaN或“DrGaN”电源开关。它集成了e模HEMT和集成的3D单片Si PMOS,并有可能使功率传输解决方案跟上未来cpu和gpu的功率密度/效率需求。180nm DrGaN器件表现出优异的RDSON(0.8mΩ-mm²)和漏损(远低于0.1mA)。研究人员将详细介绍通过层转移实现GaN和Si CMOS 的3D单片集成的新栅极最后工艺流程,其中Si CMOS晶体管的高温激活步骤在GaN MOSHEMT的栅极介电介质沉积之前完成(图7)。这解决了GaN和Si CMOS晶体管3D单片集成的主要障碍。该流程还使GaN和Si CMOS晶体管能够共享相同的后端互连堆栈,从而消除了连接内电阻并减少了掩模计数。对于30nm栅极长度的GaN MOSHEMT,器件实现了FOM=1/(RONQGG)of 0.59(mΩ-nC)-1,显示了该架构未来扩展的潜力。(Paper 9.7, “DrGaN: an Integrated CMOS Driver-GaN Power Switch Technology on 300mm GaN-on-Si with E-mode GaN MOSHEMT and 3D Monolithic Si PMOS,” H.W. Then et al, Intel)

四、高速器件

世界纪录的射频性能和低温可能性:未来太赫兹(THz)应用以及量子计算系统和外太空等低温环境中需要高速、高能效的器件。但它们运行得越快,就越难以衡量和描述它们的表现。在IEDM 2021上,苏黎世联邦理工学院展示了一种具有新颖发射极鳍片结构的InP/GaAsSb双异质结双极晶体管(DHBT),其表现出创纪录的高频性能。今年,他们将介绍在高达330 GHz的太赫兹晶体管表征和计量方法方面取得的重大进展,这使他们能够确定他们的DHBT平均频率为800 GHz,这是DHBT器件的世界纪录。此外,他们将展示任何太赫兹晶体管的第一个低温数据,显示它在50K时分别达到0.57/1.46 THz的fT/fMAX,这是任何HBT器件的世界纪录,开辟了新的太赫兹应用。(Paper 34.6, “THz InP/GaAsSb DHBTs with Record ƒAVG=800 GHz: Characterization to 330 GHz,” A.M. Arabhavi et al, ETH-Zurich/Univ. of Bordeaux)

五、成像技术的进展

CMOS成像仪的最小像素:从CMOS图像传感器(CIS)获得更高分辨率的传统方法是减小单个像素的大小。但是较小的像素更容易受到电噪声的影响,尤其是随机电报信号(RTS)的影响,以及寄生电容的影响,寄生电容降低了它们将光转换为电信号的效率。三星研究人员将展示迄今为止最小的像素为0.5μm的3层堆叠式64万像素CIS架构。该器件的一个关键特征是它使用铜对铜键合来层对层互连像素,从而精确地对齐它们,从而减小CIS的尺寸,并减少寄生电容。与早期的工作相比,像素显示RTS噪声降低了85%,光转换效率提高了67%。(Paper 40.1, “A 0.5μm pixel 3-layer stacked CMOs Image sensor with Deep Contact and In-pixel Cu-Cu Bonding Technology,” GD Ryan Lee et al, Samsung)

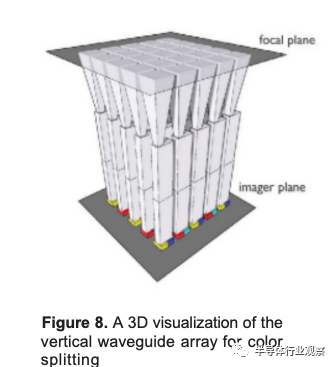

一种以亚微米像素大小渲染颜色的新方法:下一代 CMOS 成像器需要更小的像素和更高分辨率。然而,较小的像素捕获的光线较少,因此提高其分辨率很困难。捕获更多光线的一种方法是将入射光分成与不同颜色相对应的不同波长,然后调整这些波长以匹配人眼的颜色敏感度。IMEC 领导的团队将描述一种全新的方法,可以在 300 mm 晶圆上使用标准后端处理,以亚微米像素尺寸(即超出基本阿贝衍射极限)实现此目的。他们在 SiO2 矩阵中构建了 Si3N4 多模波导阵列。每个波导将不同频率的光分为对称模式和非对称模式,这些模式在波导中传播的方式不同,从而在给定频率的两种模式之间产生独特的“跳动”模式(图8)。这种跳动图案用于代表某种颜色。研究人员表示,这项技术可以进一步扩展高分辨率成像器的尺寸,最终目标是检测每个入射光子。(Paper 8.1, “ wafer Level Integrated vertical wave guide sub Diffraction Limited Color splitters,” S. Kang et al, IMEC/KU Leuven/Ghent Univ.)

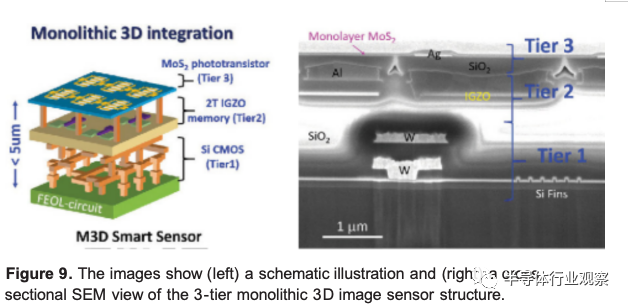

智能图像传感器:Macronix领导的团队将描述一种用于智能图像传感应用的顺序堆叠设备。他们在8英寸Si晶圆上构建了一个三层单片集成器件,包括20nm Si FinFET、基于IGZO的DRAM类器件和具有超高响应度的MoS2 TMD光电晶体管(9)。他们成功展示了硅FinFET中的逻辑反相器、NAND和NOR功能;用于存储器计算功能的长数据保持时间(>1000 s)和低功耗工作存储器;以及响应度>1A/mW和大可调光增益的5x5阵列MoS2 TMD光电晶体管。这种新型平台显示了BEOL细间距垂直互连的优势,可以实现小尺寸和超薄智能图像传感系统。(Paper 33.2, “3D Monolithically Integrated Device of si CMOs Logic, IGZODRAM-like, and 2D Mos2 phototransistor for smart Image sensing,” F.M Lee etal, Macronix/Taiwan Semiconductor Research Institute/National Tsing Hua Univ.)

六、关于不同主题的值得注意的论文

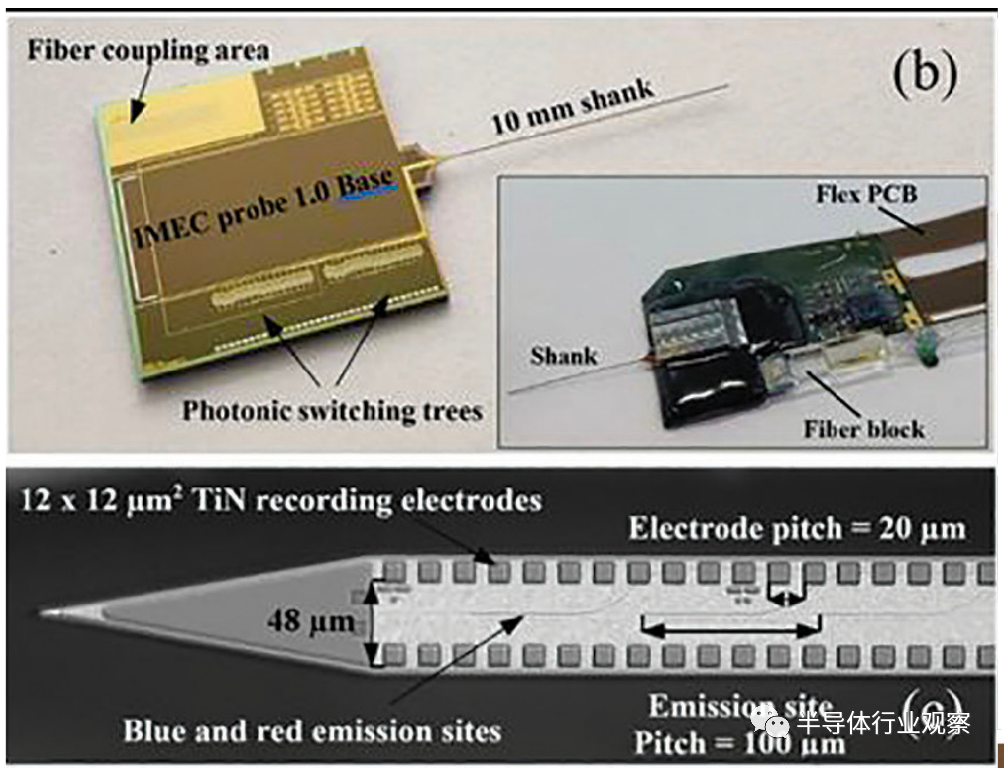

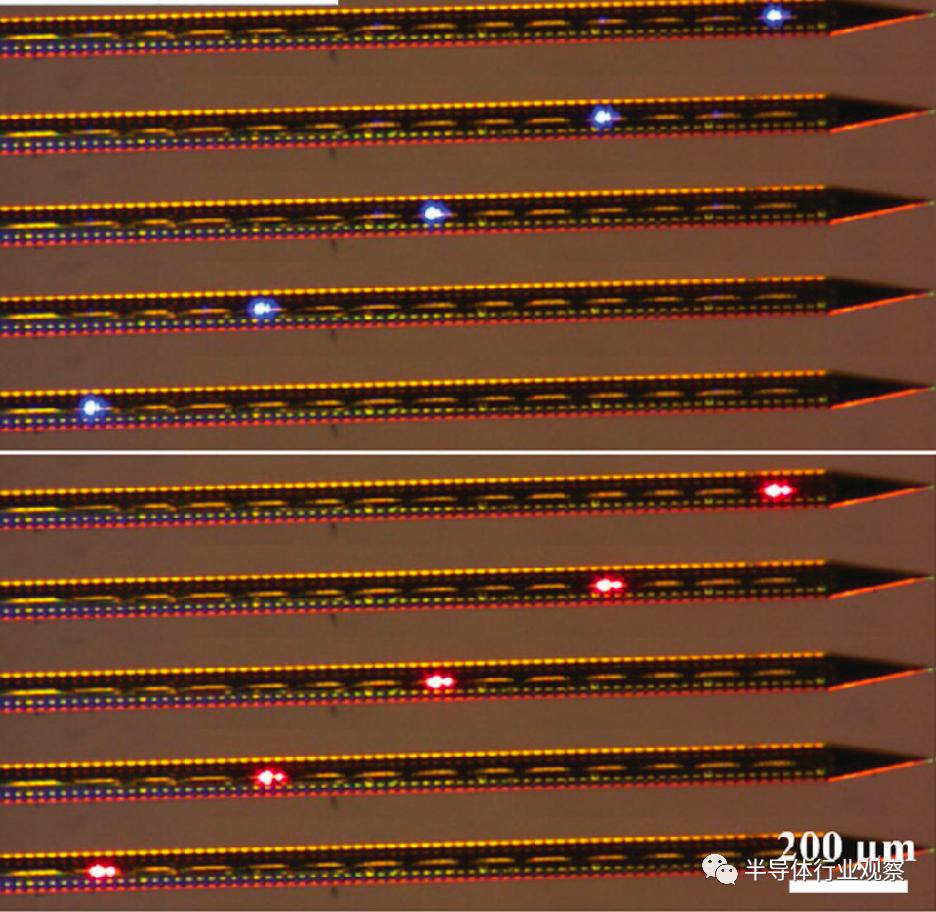

光照进大脑:IMEC的研究人员将详细介绍一个单片集成CMOS/光子学平台,能够支持无源和有源的热光开关可见光子学。它采用了基于130纳米SOI CMOS工艺的PECVD SiN波导和六层铝BEOL(图10)。他们利用这个平台展示了一种植入式基于CMOS的神经探针,该探针可以同时对大脑进行光学刺激并从中读取电信号。它集成了960个可选择电极/384个记录沟道的高密度阵列,具有14个可编程光发射位点,用于两个可见波长(450nm和638nm)。与现有的具有光传输和电记录功能的多功能神经探针相比,这些探针在双波长操作下实现了最大数量的发射器(改进了14倍);每杆电极数量增加了一个数量级(提高了10倍);以及第一次单片集成读出IC。这项技术为神经科学界提供了一个强大的工具,可以通过基于光遗传学的光学标记来研究细胞/电路特异性活动和神经调制监测。它还可以为生物传感器和超分辨率显微镜等其他应用开辟机会。(Paper25.6, “Dual-wavelength Neural prob for Simultaneous Opto-Stimulation and Recording, Fabricated in a Monolithically Integrated CMOS/Photonics Technology Platform,” P. Neutens et al, IMEC)

图 10. 顶部是完全处理过的神经探针集成电路的图像。插图是完全封装后的探针。中图是柄部的图像,显示了记录电极和光学发射点。下图是在发射点之间切换时拍摄的柄部显微镜图像。

提高基于 BEOL 的薄膜晶体管的可靠性: 在后端线(BEOL)处理过程中制造芯片布线或互连时,构建超薄 CMOS 晶体管并将其集成到芯片中,是构建未来神经形态、人工智能和其他计算应用所需的单片高集成度三维设备的一种引人注目的方法。但是,虽然由 In2O3 制成的薄膜晶体管 (TFT) 与 BEOL 加工中使用的低温技术兼容,但它们存在氧空位等缺陷,导致性能不佳和/或温度/偏压不稳定,影响其可靠性。

普渡大学领导的团队将讨论使用掺杂氟的替代沟道材料(InGaO)来中和缺陷。他们构建了兼容 BEOL 的 InGaO TFT,具有 60nm 长的超薄(约 3nm)沟道,实现了增强模式操作,并达到了此类器件中迄今为止最高的开/关电流性能(ION/IOFF 约 10-11)。它们具有 418 μA/μm 的高离子强度,以及研究人员称之为 "极高的 "温度/偏压稳定性。这项研究成果表明,掺杂剂对于氧化物基 TFT 实现更高可靠性至关重要,尤其是在这些器件中使用氟等阴离子(带负电荷)与通常使用的阳离子(带正电荷)掺杂剂相比的好处。(Paper 41.1, “Fluorine Anion-Doped Ultra-Thin InGaO Transistors Overcoming Mobility-Stability Trade-Off,” J. Zhang et al, Purdue Univ./Xiamen Univ.)

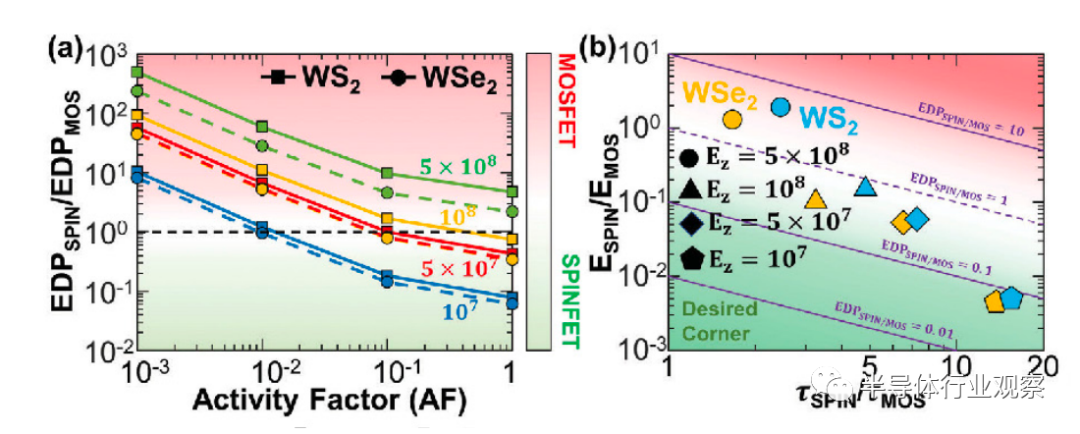

共同设计二维逻辑电路的材料和器件:自旋场效应晶体管是一种利用电子自旋态而非带电层来控制电流的晶体管。尽管具有广泛自旋轨道耦合和奇特结构/电气特性的各种二维材料对设计基于自旋的晶体管和互连器件很有吸引力,但由于缺乏对自旋动力学的透彻了解,二维自旋逻辑无法实际实现。在 IEDM 上,由加州大学圣巴巴拉分校领导的团队将详细介绍一种新颖的材料-器件协同设计框架,该框架模拟了许多不同的相关自旋弛豫/相消机制,以便为材料和器件工程师提供切合实际的设计指南,推动最新技术的发展(图 11)。作者特别揭示了二维材料石墨烯的自旋扩散长度大于 25 μm,他们还表明,基于优化二维自旋场效应晶体管的电路在能量延迟方面比其 MOSFET 同类器件高出一个数量级,在能效方面高出两个数量级。(Paper 3.4, “A Materials-Device Co-Design Framework for Re-alizing Ultra Energy-Efficient All-2D-Spin-Logic Circuits with 2D-Materials,” S. Zhang et al, UC- Santa Barbara/Zhejiang Univ.)。

图 11.上图显示了各种能量-延迟-产品(EDP)基准测试结果:左图是SpinFET与MOSFET的EDP比率,使用p型WS2和WSe2沟道,作为电路活动因子(AF)的函数,在垂直电场(EZ)为107 V/m、5×107 V/m、1×108 V/m和5×108 V/m在100K的条件下。

黑色虚线(比率 = 1)划分了 SpinFET(绿色)和 MOSFET(红色)显示出更多 EDP 优势的区域。右图比较了 p-WS2 和 p-WSe2 在 AF=1 时数字电路中 SpinFET 和 MOSFET 的能耗 (E) 和开关延迟比。

来源:SEMI半导体研究院